# A 2.4-6.0 GHz High Gain LNA for Broadband Applications.

## Bhushan R. Vidhale, Dr.M.M.Khanapurkar

Dept. of Electronics and Telecommunication Engineering, GHRCE, Nagpur (M.S.), India Research Scholar, GHRCE, Nagpur (M.S.), India

**Abstract:** In this work 0.18  $\mu$ m CMOS is used to achieve low-characteristics and best performance of in the band of 2.4 GHz to 6.0 GHz. Here simulation tool is used for simulation of lumped components with an inductor less concept. Designed broadband LNA supports multi standard wireless applications with High gain and low noise figure.

Due to the accurate calculation and the proper impedance matching, the results are the forward gain  $(S_{21})$  is 18dB and Noise figure is less than 2.4dB. Input impedance  $(S_{11})$  and output impedance  $(S_{22})$  also represent good performance. Third order intercept point is -5.25dBm is obtained with the linearity and the performance is good, so that the LNA circuit gives good availability for wireless applications and broadband applications.

Keywords: LNA, gain, noise figure, s-parameters, dissipated power.

#### I. Introduction

Increasing demands of higher data transfer rates and global mobility in current wireless communication environment has led to the development of the Third Generation (3G) mobile communication standard. Nowadays, large operators and small operators, served both developed and emerging market, which give benefits over 3G technologies. Communication system containing transmitter and receiver ,at the receiver end it contain attenuation and also interference. The signal range is in mili-volt range hence hamper the operation of demodulator; so it is require to boost-up the signal and the feeding it to the demodulator. Here amplifier increases the gain but also increase the noise. Therefor the LNA with less noise is required which is at the receiver side.

This paper describes the multi-standard structure of low noise amplifier as a bandwidth extension technique. For a multiple band Receiver, one requirement is to use tuned RF front-ends which is based on broad-band, and also tunable LNAs.

#### Applications

#### II. Overview On Aroad-Band

Immersive virtual environments have been moving towards to practical system from research from primarily research. Wireless communications and its application increasing day by day. Basic idea of this development is to give digital signal processing (DSP) in the wireless communication field. Where the CMOS technology give the integrated functionality of DSP, basically current front-end circuits uses mixture of semiconductor technologies, here by using GaAs to SiGe, on single chip the integration of communication system is possible. Recent advancements in CMOS technology, which are Radio Frequency (RF) CMOS Integrated Circuit (IC) it provide on a single chip the potential solution. Design and development of a new reconfigurable LNA architecture is believed to be one of the pioneering attempts in providing new trend of designing LNA for multi-standard multi-band RF receiver system. There is Strong demands for multi-standard multi-band devices with more functionality (i.e. video call, games, email etc.) the compact system design in wireless mobile device is given by RFIC. Nowadays, mobile devices support multiple functions by using several standards.

#### Low Noise Amplifier

## III. Designing Steps For Broad-Band

When the LNA circuit is cascaded to the second stage, the inter stage parasitic reactance attenuated by the desired bandwidth of the low noise amplifier. Now a days, the designed LNAs used the cascode topology which gives lower current and also provide the options to select the band of interest. If it faces some difficulty then in that case, the Broad-band LNAs are choose and designed to cover the maximum number of standards.

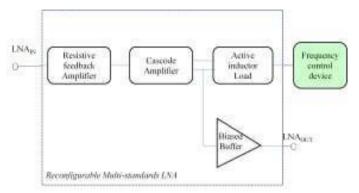

However, design based on inductive greatly affects the silicon area which is of a higher fabrication cost. Figure 3 shows the multi standard LNA which is based on broad band. Which contain a resistive feedback stage and next to that a cascode amplifier which a high gain. A resonant load is provided by the active inductor

,which is controlled by a biased varactor device further which select the desired frequency band. Mentioned stages will be described as follows.

Figure 1: Shows Block diagram of the designed LNA

At the front end of the receiver one of the critical block is LNA. On the performance of the LNA the bandwidth of signal, noise figure, and gain and power consumption of the entire system depends. The proposed LNA consists of following stages.

#### A. Resistive feedback amplifier stage

One of the optimal topology is the resistive feedback amplifier due to its simplicity, also it has small area and comparative low noise figure than other topologies.

#### **B.** Cascode amplifier stage

Stability require good input and good output which is provided by the cascade amplifier which also give the high gain.

#### C. Active inductor load and Differential LNA

In the active inductor load and differential LNA consists of two transconductors connected which are back-to-back. In which the differential pair implement the first transconductor. On the other hand current mirror amplifier implements the second transconductor.

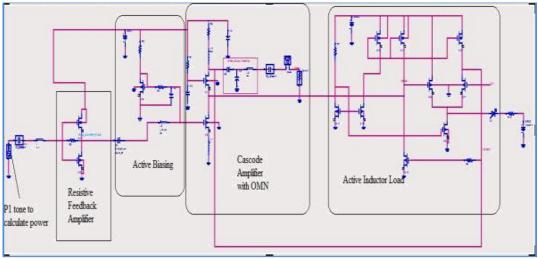

#### IV. Schematic View And Schematic Design For Low Noise Amplifier

The LNA circuit, consists of NMOS and PMOS transistors, so that it forms CMOS inverter. Biasing circuitry for LNA is designed by usingactive lumped component. Due to which the equivalent value of transconductance get increased from one level to another level by using dc current. The first part shows Resistive feedback Amplifier which the combination of two NMOS transistors to prevent from buffering in the circuit. Proper impedence matching and high gain is provided by the resistive feedback amplifier. Where as vertical transistor forms second stage i.e cascade amplifier. Also the resistors  $R_{c1}$  and  $R_{c2}$  are used for active biasing purpose. Active inductor is used at last that is at third stage which is used to supply load to cascade stage. Two transconductors resistance  $R_1$  can be inserted which increase the quality factor of active inductor and for biasing resistance R2 is used.

Figure 2: Schematic of Broad-band LNA circuit

### V. Schematic Simulation Results For Lna Design: 2.4 Ghz To 6.0 Ghz

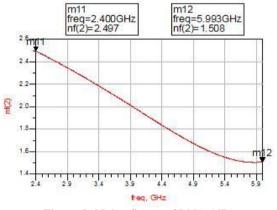

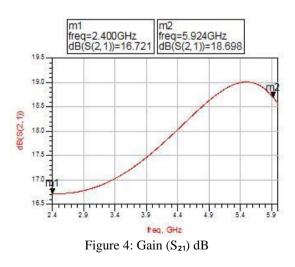

The amplifier is presented with high gain,low noise figure, and with input/output return loss in designing of multi-stage cascaded types of LNA. On the basis of simulation results the integrated circuit give the LNA with low power consumption and less number of input/output return losses. By using Agilent's ADS LNA schematic is simulated by using 0.18 $\mu$ m CMOS technology which gives (16-18) dB of gain (S<sub>21</sub>), less than 2.4dB noise figure (NF).Return losses are also good. As there is tradeoff between low noise figure and return loss; the matching is shown in schematic of LNA. The power dissipation in the whole circuit is 25Mw from the supply of 1.8V.Also 1dB compression Gain for this LNA at Pin of - 13mW is 15dB with Pout of 2mW .While 3dB gain is 13dB at Pin-9.7mW with Pout of 4mW.

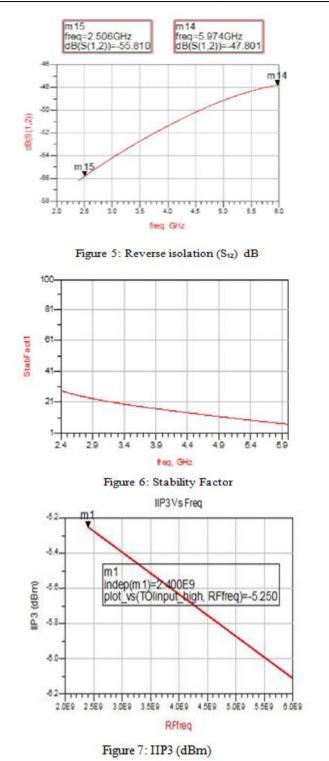

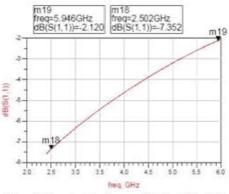

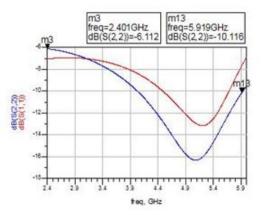

This proposed a new methodology for designing LNA for relatively broad-band system to support multi-standard and multi-band with just one single circuit implementation. The forward gain ( $S_{21}$ ) achieved is (16.72-18.69) dB at the frequency range from (2.4-6.0) GHz as shown in Figure. Better bandwidth with the gain above 10dB is obtained.. The reverse isolation ( $S_{12}$ ) obtained from the simulation is good which is more than the typical value which is normally -30 dB ;( - 55.8 to - 47.8) dB. The input losses and output losses,  $S_{11}$  and  $S_{22}$  of LNA are shown in Figure. For  $S_{11}$ , the simulations result produced an input return loss of -7 dB at the center frequency of 2.4GHz. For  $S_{22}$ , simulation result produced a value of (-6.0 to -10) dB at the frequency range from (2.4-6.0) GHz as shown in Figure. Therefore, by adjusting resistor and capacitor optimization is done. The output return loss achieved, however, is well below -10 dB along the bandwidth. Also noise figure less than2.4dB is obtained.

A two-tone test for the third-order intercept point is used to check the linearity requirement. For which The two tones were applied at frequencies of 2.4 GHz and 6.0 GHz respectively which contain equal power. The achieved IIP3 is -5.25 dBm and is shown in Figure. This achieved value has specification and also fulfill linearity requirements. The less amount of current in circuit is obtain by choosing best IIP3 value. The following table shows comparison with previous work which has been done for the low power LNA which support wireless communications in the frequency band of 2.4 GHz to 6.0 GHz.

| LNA parameters    | Simulation results |         |

|-------------------|--------------------|---------|

| Frequency Band    | 2.4 GHz            | 6.0 GHz |

| Supply voltage    | 1.8 \              | /       |

| S <sub>11</sub>   | -7.0 dB            |         |

| S <sub>12</sub>   | -55.8 dB           | -47.8dB |

| S <sub>21</sub>   | 16.72 dB           | 18.69dB |

| S <sub>22</sub>   | -6.0 dB            | -10 dB  |

| Noise figure      | < 2.4 dB           |         |

| Stability Factor  | More than 1.0      |         |

| 1 dB Gain         | 15.73 dB           |         |

| 3 dB Gain         | 13.75 dB           |         |

| Power Dissipation | 25 mW              |         |

| IIP3              | -5.25dBm           |         |

Figure 3: Noise figure of LNA (dB)

Figure 8: Input reflection coefficients (S11) dB

Figure 8: Output reflection coefficients (Szz) dB

#### VI. Conclusion And Disscussion

The amplifier is presented with high gain ,low noise figure, and with input/output return loss in designing of multi-stage cascaded types of LNA. On the basis of simulation results the integrated circuit give the LNA with low power consumption and less number of input/output return losses. By using Agilent's ADS LNA schematic is simulated by using 0.18 $\mu$ m CMOS technology which gives (16-18) dB of gain (S<sub>21</sub>), less than 2.4dB noise figure (NF). As there is tradeoff between low noise figure and return loss; the matching is shown in schematic of LNA. The power dissipation in the whole circuit is 25Mw from the supply of 1.8V.Also 1dB compression Gain for this LNA at Pin of -13mW is 15dB with Pout of 2mW .While 3dB gain is 13dB at Pin-9.7mW with Pout of 4mW.

In addition, the results achieved are representation of the trade-off made between s-parameters, linearity, and NF and power consumption. However, some of the parameters still need an improvement i.e. Gain. This could be done by improving the circuit power by increasing the current of the circuit. But this action should be taken carefully as not to contradict with the low power design. Therefore, the proposed RF receiver architecture could solve this problem by using a reconfigurable concept. The reconfigurable architecture will have the capability to support multiple standards in one system but with fewer components which results in simpler, more compact, less expensive and less power consumption. Finally, the research carried out in this work has specifically achieved the followings results:

- i. The RF receiver system simulation which has been carried out to find the mutual relationship between RF receiver system and RF components specifications provides the minimum and optimum requirement of the LNA's specifications. This will help in developing better RF system.

- ii. The development and implementation of Broad band LNAs provides a new approach for designing the multi-standard multi-band LNA for a relatively system especially for mobile communication standards.

- iii. The development and implementation of the reconfigurable multi-standard multiband LNA will further provide new methodology in the design of multi-standard LNA for multi-standard system.

- iv. This technique which was also employed by the reconfigurable LNA consumes relatively lower power consumption compared to the design which uses buffer circuit for matching purposes.

#### References

- [1]. S. Woo and W. Kimal, "A 3.6 mW differential common gate CMOS LNA with positive -negative feedback,"inProc.IEEEISSCC,Feb.2009,pp.218–219. [2]I.R.ChamasandS.Raman,"Analysis,design,andX-band implementation of a self-biased active feedback boosted common-gate CMOS LNA," IEEE Trans.

- [2]. Microw. Theory Tech., vol. 57, no. 3, pp.542–551, Mar. 2009.

- [3]. J. Schleeh, H. Rodilla, N. Wadefalk, P. A. Nilsson, and J. Grahn, "Characterization and modeling of cryogenic ultra-low noise InP HEMT," IEEE Trans. Electron Devices, 2013, to be published.

- [4]. Monali Khune and Bhushan Vidhale," Analysis and Design of CS-LNA using 0.18μm CMOS Technology", IJVES Vol 05, Article 02229; March 2014, ISSN: 2249 6556.

- J.Liu, H.Liao, and R.Huang, "0.5 Vultra-low power wideband LNA with forward body bias technique," Electron. Lett., vol. 45, no. 6, pp.289–290, Mar. 2009.

- [6]. H.G. Dehrizi, J. Haddadnia, "A great Ultra Wideband (3.1– 10.6-GHz) LNA in 0.18-μm (CMOS) for UWB pulseradiosystemsapplications," 9th International Multi-Conference on Systems, Signals and Devices (SSD), pp.1-4, Mar. 2012.

- [7]. Ching-Piao Liang, Pei-Zong Ra, Tina-Jian Huang, and Shyh -Jong Chung, "Analysis and Design of Two Low-Power Ultra -Wideband CMOS Low-Noise Amplifiers With Out-Band Rejection," IEEE Tran. Microw. Theory Tech., vol. 58, no. 2, pp. 277-286, Feb. 2010.

- [8]. Jigisha Sureja, Shruti Oza, Jitendra Thathagar3," A 0.1-3 GHz Low Power Cascode CS LNA using 0.18µm CMOSTechnology",20121stInternationalConferenceon Emerging Technology Trends in Electronics, Communication and Networking.

- [9]. G. Gonzales, Microwave Transistor Amplifiers: Analysis and Design, 2nd ed., Prentice Hall, Upper Saddle River, NJ, 1997, 1-104.

- [10]. Reinhold Ludwig and Povel Bretchko, RF Circuit Design: Theory and Applications, 2nd ed., 2002, 168-193 & 405-532.

- [11]. Jhin-Fang Huang, Ming-Chun Hsu, Jiun-Yu Wen and Ron -YiLiu"ChipDesignofanUWB, HighGainand Low Noise Amplifier for Wireless Applications", 2011 Third

- [12]. International Conference on Communications and Mobile Computing, IEEE 2011.

- [13]. D. M. Pozar, Microwave Engineering, Second Edition, John Wiley & Sons Inc., USA, 1997, 196-222.

- [14]. Hari Varma, Nisha Kunder, Kerman Daruwalla. Low Noise Amplifier Design Project; ELE 791 Microwave Transistor Amplifiers. pp: 1-22.

- [15]. Trang Thai;Low Noise Amplifier Design for operating frequency of 4.2 GHz; ECE 4415a Project Dec 12, 2007.

- [16]. "RF Microelectronics", Behzad Razavi. Prentice Hall, NJ, 1998.

- [17]. Thomas H. Lee.,"The Design of CMOS Radio Frequency Integrated Circuits", Cambridge University Press, 1998.

- [18]. A.P. Adsul ,Dr. S.K. Bodhe , "A Low-Noise Amplifier Design for 3.1-10.6 GHz Impulse Radio Ultra WidebandReceivers", IEEE2013.

- [19]. Guillermo Gonzalez, "Microwave Transistor Amplifiers", PrenticeHall, 1984.

- [20]. Zhichao Zhang, Anh. Dinh, Muhammd khan, Li Chen and Hemachandra Gorla, "A 0.3GHz-3.3GHz Highly Linear CMOS LNA for Multimode Applications", IEEE 2012.

- [21]. Design of Analog CMOS Integrated Circuits B. Razavi

- [22]. LNA Design Trade-Offs in the Working World Free scale