# A noval Approch of area efficient and fast radix 2<sup>3</sup> means (8) modified booth multiplier

# Preety janweja<sub>1</sub>, Vipin gupta<sub>2</sub>

1.Master of technology (scholar), Suresh gyanvihar university, Jaipur, india 2. Assistant professor, suresh gyanvihar university Jaipur, india

**Abstract:** Array multiplier occupies larger area so MBE is engaging approach to style efficient multiplier. This paper presents new concept which is able to optimize the realm and speed of information calculation. The modified Booth Encoder circuit generates half the partial products in parallel. By extending sign little bit of the operands and generating an extra partial product the SUMBE multiplier obtained. Parallel Prefix Adder wont to speed up the number operation. The new approach of 2'S complement has been introduced during this paper to cut back the realm of MBE.

Keywords: MBE, Radix 2n, Parallel Prefix adder, new approach of 2's Complement Method.

# I. Introduction

In digital computing systems multiplication operation, the multiplication operation consists of manufacturing partial product then adding these partial product the ultimate product is obtained. therefore the speed of the multiplier factor depends on the quantity of partial product and also the speed of the adder. Since the multipliers have **a** major impact on the performance of the complete system, several high performance algorithms and architectures are planned. The terribly high speed and dedicated multipliers square measure employed in pipeline and vector computers. The high speed Booth multipliers and pipelined Booth multipliers square measure used for digital signal process (DSP) applications like for multimedia system and communication.

High speed DSP computation applications like quick Fourier rework (FFT) need additions and multiplication. The papers presents a style methodology for top speed Booth encoded parallel multiplier factor. For partial product generation, **a** replacement changed Booth secret writing (MBE) theme accustomed improve the performance of **ancient** MBE schemes. However this multiplier factor is simply for signed range multiplication operation.

The conventional changed Booth secret writing (MBE) generates AN irregular partial product array thanks to the additional partial product bit at the smallest amount vital bit position of every partial product row. so papers presents a straightforward approach to come up with a daily partial product array with fewer partial product rows and negligible overhead, thereby lowering the quality of partial product reduction and reducing the world, delay, and power of MBE multipliers. however the downside of this multiplier factor is that It perform just for signed range operands. The modified-Booth formula is extensively used for high-speed multiplier factor circuits. Once, once array multipliers were used, the reduced range of generated partial product considerably improved multiplier factor performance. In styles supported reduction trees with index logic depth, however, the reduced range of partial product contains a restricted impact on overall performance. The Baugh-Wooley formula could be a completely different theme for signed multiplication, however isn't thus wide adopted as a result of it should be difficult to deploy on irregular reduction trees. once more the Baugh-Wooley formula is for less than signed range multiplication. The array multipliers and Braun array multipliers operates solely on the unsigned numbers. Thus, the necessity of the trendy computing system could be  $\mathbf{a}$  dedicated and really high speed multiplier factor unit which will perform multiplication operation on signed vet signed numbers, during this paper we have a tendency to designed and enforced a fanatical multiplier factor unit which will perform High Speed multiplication operation on each signed and unsigned numbers that occupy lesser space, and this multiplier factor is named as SUMBE multiplier factor.

## II. Review Of Literature

In the previous paper "High speed changed Booth Encoder number for signed and unsigned numbers" 2012 fourteenth International Conference on Modelling and Simulation, It is **a** robust rule for signed-number multiplication, that treats each positive and negative numbers uniformly .For the quality add-shift operation, every number bit generates one multiple of the number to be side to the partial product. If the number is extremely massive, then an outsized variety multiplicands need to be side. during this case the delay of number is decided primarily by the amount of additives to be performed. If there's how to scale back the amount of the additions, the performance can bounce back. Booth rule could be **a** methodology that may cut back the amount of number multiples. For a given vary of numbers to be diagrammatic, the next illustration base ends up in fewer digits. Since a k-bit binary variety may be understood as K/2-digit radix-4 variety, a K/3-digit radix-8 variety, and so on, it will handle over one little bit of the number in every cycle by exploitation high base multiplication. this can be shown for Radix-4 within the example below.

| Multiplicand    | A =  | • • • •                              |                   |

|-----------------|------|--------------------------------------|-------------------|

| Multiplier      | B =  | $(\bullet \bullet)(\bullet \bullet)$ |                   |

| Partial product | bits | • • • •                              | $(B_1B_0)_2 A4^0$ |

|                 |      | • • • •                              | $(B_3B_2)_2A4^1$  |

| Product         | P =  |                                      |                   |

Radix-4 multiplication in dot notation.

As shown within the figure higher than, if multiplication **is** finished in number four, in every step, the partial product term (Bi+1Bi)2 A must be shaped and accessorial to the additive partial product. Whereas in radix-2 multiplication, every row of dots within the partial product matrix represents zero or a shifted version of a requirement be enclosed and accessorial.

Table 1below is employed to convert a binary range to radix-4 range.

Initially, a "0" is placed to the correct most little bit of the number. Then three bits of the number is recoded in step with table below or in step with the subsequent equation:

Zi = -2xi + 1 + xi + xi - 1

| Table .1 Radix-4 Booth recoding |   |                  |                  |  |  |  |  |  |  |

|---------------------------------|---|------------------|------------------|--|--|--|--|--|--|

| X <sub>i+1</sub>                | Х | X <sub>i-1</sub> | Z <sub>i/2</sub> |  |  |  |  |  |  |

| 0                               | 0 | 0                | 0                |  |  |  |  |  |  |

| 0                               | 0 | 1                | 1                |  |  |  |  |  |  |

| 0                               | 1 | 0                | 1                |  |  |  |  |  |  |

| 0                               | 1 | 1                | 2                |  |  |  |  |  |  |

| 1                               | 0 | 0                | -2               |  |  |  |  |  |  |

| 1                               | 0 | 1                | -1               |  |  |  |  |  |  |

| 1                               | 1 | 0                | -1               |  |  |  |  |  |  |

| 1                               | 1 | 1                | 0                |  |  |  |  |  |  |

#### Table Multiplier recoding

| 0      | 0      | 0      | +0*multiplicand                    |

|--------|--------|--------|------------------------------------|

| 0<br>0 | 0<br>1 | 1<br>0 | +1*multiplicand<br>+1*multiplicand |

| 0      | 1      | 1      | +2*multiplicand                    |

| 1      | 0      | 0      | -2*multiplicand                    |

| 1      | 0      | 1      | -1*multiplicand                    |

| 1      | 1      | 0      | -1*multiplicand                    |

| 1      | 1      | 1      | -0*multiplicand                    |

Here  $-2^*$  multiplicand is really the 2s complement of the number with the same left shift of 1 bit position. Also,  $+2^*$  multiplicand is that the number shifted left one bit position that is corresponding to multiplying by two.

To enter 2\*multiplicand into the adder, associate (n+1)-bit adder is needed. during this case, the number is offset one bit to the left to enter into the adder whereas for the low-order number position a zero is additional. on every occasion the partial product is shifted **2** bit positions to the correct and therefore the sign is extended to the left.  $\pm$

During every add-shift cycle, completely different versions of the number square measure additional to the new partial product depends on the equation derived from the bit-pair coding table on top of

## III. Proposed Design:

**Step 1:**-To produce quick or high speed multiplier factor we'd like some quickest adding application, we've got already reduced no. of partial product. thus currently we've got less no. of operands for adding, AN economical methodology of addition (Parallel prefix Adder) are going to be implement in partial product addition. Parallel Prefix Adder Parallel prefix adder is that the most versatile and wide used for binary addition. Parallel Prefix adders square measure best suited to VLSI implementation. Numbers of parallel prefix adder structures are planned during this style meant to optimize space, fan-out, logic depth and entomb connect count. This paper presents **a** replacement approach to revamp the fundamental operators utilized in parallel prefix architectures.

Step 2:- To form space economical multiplier factor we'd like some effective algorithmic rule for 2's complement method in signed no. we've got already mentioned regarding thet MBE work for signed and unsigned no.

New approach of 2's complement no. Let us take into account the number knowledge A to be used with the negative partial product factors. To calculate the 2's complement initial is to inverse all the bits of the information A denoting them as Abar. currently perform "Exclusive OR" (XOR) operation on Abar(0) with 1'b1, Abar(1) xor Abar(0), Abar(2) xor Abar(1) then on until a 1'b0 is found whereas traversing the information bits A(i). Once 1'b0 is arrived keep the remaining bits because it is without any amendment.

Lets USA take into account Associate in Nursing example wherever A=10101000, then 2's complement of A be denoted as A2\_c\_bar, then

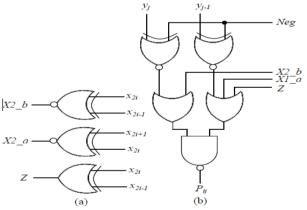

Fig. 1. The Encoder and Decoder for the new MBE scheme. (a) Simple encoder (b) Decoder.

Step 1: A bar=01010111. Step 2: A2\_c\_bar (0) = 1 xor 1 = 0A2\_c\_bar (1) = 1 xor 1 = 0A2\_c\_bar (2) = 1 xor 1 = 0A2\_c\_bar (3) = 1 xor 0 = 1A2\_c\_bar (4) = A'4 = 1A2\_c\_bar (5) = A'5 = 0A2\_c\_bar (6) = A'6 = 1A2\_c\_bar (7) = A'7 = 0 *A noval Approch of area efficient and fast radix 2*^3 *means (8) modified booth multiplier*

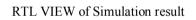

Simulation RESULT:

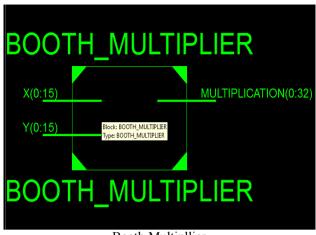

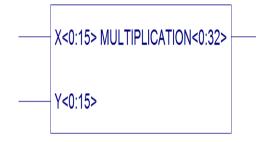

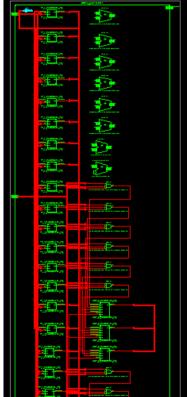

# TOP view of 16-bit booth multiplier

| <b>\$</b> .                | Msgs                                      |                  |            |           |           |                        |           |           |                   |           |           |           |               |

|----------------------------|-------------------------------------------|------------------|------------|-----------|-----------|------------------------|-----------|-----------|-------------------|-----------|-----------|-----------|---------------|

| 🛃 🁍 /booth_multiplier/X    | -16'd31967                                | X                |            |           |           |                        |           |           | -31967            |           |           |           |               |

| ₽-\$ /booth_multiplier/Y   | 16'd4660                                  | X                |            |           |           |                        |           |           | 4660              |           |           |           |               |

| 🗟 💠 /booth_multiplier/M    | -33'd149490508                            | 0                |            |           |           |                        |           |           | -1494905          | 08        |           |           |               |

| 🛃 /booth_multiplier/PAIR   | . {3h0} {3h2} {3h                         | <u>{3hx} {</u> 3 | hx} {3hx}  | {3hx} {3  | hX} {3hX  | {3ħX} {3               | hX}       |           | {3h0} {3          | h2} {3h1  | {3h4} {3  | h1} {3h6  | {3h2} {3h0    |

| E-🔶 /booth_multiplier/MBIT | {3h0} {3h1} {3h                           | {3h0} {3         | ho} {3ho}  | {3h0} {3  | h0} {3h0  | {3h0}{3                | h0}       |           | { <b>3h</b> 0} {3 | h1} {3h1  | {3h6}{3   | h1} {3h7  | {3h1} {3h0    |

| 🖅 🔶 /booth_multiplier/PP   | {19 <sup>°</sup> h00000} {19 <sup>′</sup> | {19h000          | 00} {19h0  | 0000}{19  | h00000}   | 19 <sup>°</sup> h00000 | ) { 19h00 | 000} {19h | 00000}{1          | 9'h00000) | {19h0000  | 0}        |               |

| 🖅 👌 🕒 📴 🗄                  | {19'h00000} {19'                          | <u>{19h000</u>   | 00} {19h0  | 0000} {19 | h000000}- | 19 <sup>°</sup> h00000 | ) {19h00  | 000} {1   | (19h000           | 0) {19h7  | 8321} {19 | h78321}   | 19°h0F988} {  |

| ₽-♦ /booth_multiplier/TP   | {19'h00000} {19'                          | {19h000          | 00} { 19h0 | 0000}{19  | h00000}-  | 19°h00000              | )}{19h00  | 000} {1   | {19h000           | 0} {19h7  | 8321} {19 | h78321}{  | 19h0F98E} {   |

| ₽-♦ /booth_multiplier/TP   |                                           | {19h000          | 00} {19h0  | 0000}{19  | h00000}   | 19°h00000              | )}{19h00  | 100} {1   | {19h000           | 0) {19ħ7  | 8321} {19 | h78321}{  | 19740F986E} { |

| A booth multiplier/TP      | {33h1FFF80000}                            | (33h000          | 1000003 (2 | 2H00000   | 10003 (33 | 60000000               | nn3 (33hr | 0000      | (33h1FFF          | 800003 (  | 3h1FFFF   | 10843 (33 | 600007cmE03   |

Waveform result.. A= 31967, b= 4660 output= -149490508

#### IV. Conclusion

We conclude that multiplication is done by different methods. In booth encoding the multiplication is done by 2's compliment and Modify booth encoding multiplication method is done by XOR'ing the bits means by using gate method. So when we were using 2's compliment the number of gates used **5,563**. And when we using gate method the number of gates used **5,038** ...so by new technique we can reduce no. of gates and by reducing number of gates we can reduce Area in efficient amount.

#### V. Future scope

In future scope we can use pipelined architecture in booth multiplier so with decreasing the area we can also decrease the delay.

#### References

- W. -C. Yeh and C. -W. Jen, "High Speed Booth encoded Parallel Multiplier Design," IEEE transactions on computers, vol. 49, no. 7, pp.692-701, July 2000.

- [2]. Shiann-Rong Kuang, Jiun-Ping Wang, and Cang-Yuan Guo, "Modified Booth multipliers with a Regular Partial Product Array," IEEE Transactions on circuits and systems-II, vol 56, No 5, May 2009.

- [3]. Li-Rong Wang, Shyh-Jye Jou and Chung-Len Lee, "A well-structured Modified Booth Multiplier Design" 978-1-4244-1617-2/08/\$25.00 ©2008 IEEE.

- [4]. Soojin Kim and Kyeongsoon Cho "Design of High-speed Modified Booth Multipliers Operating at GHz Ranges" World Academy of Science, Engineering and Technology 61 2010.

- [5]. Magnus Sjalander and Per Larson-Edefors. "The Case for HPM-Based Baugh-Wooley Multipliers," halmers University of Technology, Sweden, March 2008.