# Design and Implementation of Feasible Direct Digital Synthesizer to Eliminate Manual Tweaking

Snehal Gaikwad<sup>1</sup>, Kunal Dekate<sup>2</sup>

1 (E&TC, D.M.I.E.T.R., Wardha, Nagpur University, India) 2 (Electronics, G.H.R.C.E., Nagpur, Nagpur University, India)

**Abstract:** This paper presents design and simulation of the programming model of optimal and feasible Direct Digital Synthesizer that eliminates the need for the manual tuning and tweaking related to component aging and temperature drift in analog synthesizer solutions. A Direct Digital Synthesizer is a measure part o Digital Down Converter where the DDC (Digital Down converter) has become a cornerstone technology in communication systems. Digital Down Converter (DDC) is key component of RF systems in communications, sensing, and imaging. This paper also evaluates the performance of DDS under various programming parameters and finally performs the realization of DDS using Virtex II Pro.

**Keywords:** Theory of DDC, Direct Digital Synthesizer (DDS), Performance of Direct Digital Synthesizer and Simulation Results.

## I. Introduction

Digital down Converter (DDC) is key component of RF systems in communications, sensing, and imaging. Digital radio receivers often have fast ADC converters to digitize the band limited RF or IF signal generating high data rates; but in many cases, the signal of interest represents a small proportion of that bandwidth. To extract the band of interest at this high sample rate would require a prohibitively large filter. A DDC allows the frequency band of interest to be moved down the spectrum so the sample rate can be reduced, filter requirements and further processing on the signal of interest become more easily realizable. A fundamental part of many communications systems is Digital Down Conversion (DDC). A Digital down Converter is basically complex mixer, shifting the frequency band of interest to baseband. The DDC is typically used to convert an RF signal down to baseband. It does this by digitizing at a high sample rate, and then using purely digital techniques to perform the data reduction.

### 1.1. Overview of the DDC implementation

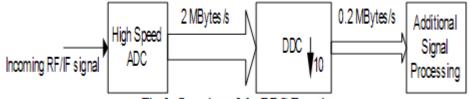

Fig. 1: Overview of the DDC Function

Consider a signal lying in the range 10-20 KHz. The signal bandwidth is 10 KHz. However, it is often digitized with a sampling rate over 1 M samples per Second, representing in the region of 2Mbyte/second. The DDC allows us to select the 10-20 KHz band, and to shift its frequency down to base-band and in doing so reduce the sample rate, with a 10 KHz bandwidth, a sample rate of 100 KHz would be fine - giving a data rate of only 0.2Mbyte/second. This is shown in Fig.1.

### II. DDS (Direct Digital Frequency Synthesizer)

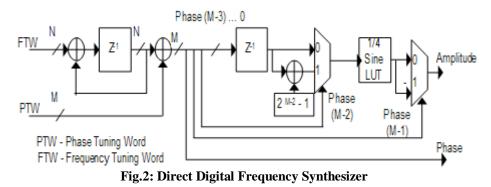

The DDS (Digital Direct Synthesizer) is an implementation of a direct digital frequency synthesizer (DDS) (also called Number Controlled Oscillator, NCO) which produces a sine wave at the output with a specified frequency and phase (adjustable at run time). The resolution of the Frequency Tuning Word (FTW), the phase and the amplitude are defined separately. While the FTW resolution can be set by the generic ftw\_width, phase and amplitude resolution are defined as constants phase\_width and ampl\_width in the separate package sine\_lut\_pkg. This is generated by a Matlab script (sine\_lut\_gen.m), the m-files are described in their headers.

The nomenclature of the files is sine\_<phase\_width>\_x\_<amplitude\_width>\_pkg. hd. By adding one of these files to the project, the resolution of phase and amplitude is automatically defined. The function of the DDS is to generate the frequency equal to the sampling frequency of the first stage. The figure 2 shows the implementation of the DDS. A direct digital synthesizer operates by storing the points of a waveform in digital format, and then recalling them to generate the waveform. The rate at which the synthesizer completes one waveform then determines the frequency <sup>[1], [2].</sup>

### 2.1. Performance Details of DDS

The frequency and phase of the DDS can be controlled using the FTW (Frequency Tuning Word) and PTW (Phase Tuning Word).

The output frequency will be determined by the FTW.  $\mathbf{F}_{dds} = (FTW/2^{(N-M)})^*(F_{clk}/(2^M))$  or  $\mathbf{F}_{dds} = FTW^*F_{clk}/2^N$

Where  $F_{clk} = Clock$  Frequency

The initial phase can be controlled by PTW.

$\Phi_{dds} = (PTW/2^M) * 2 * pi$

Match the DDS frequency to the sampling frequency so that the spectrum gets shifted towards DC (0 Hz).

#### III. **Results**

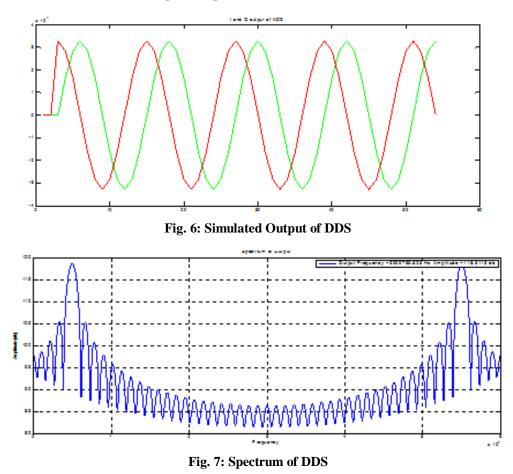

### 3.1. Simulation results for DDS

Sampling Frequency : 60 MHz

| TABLE 1: Parameters used for DDS module: |                |            |       |       |  |  |  |  |  |  |  |

|------------------------------------------|----------------|------------|-------|-------|--|--|--|--|--|--|--|

| Parameter                                | Parameter Name | Data Types | Value | Units |  |  |  |  |  |  |  |

| Frequency Tuning Word                    | FTW_WIDTH      | Integer    | 11    | Bits  |  |  |  |  |  |  |  |

| Phase Tuning Word                        | PHASE_WIDTH    | Integer    | 9     | Bits  |  |  |  |  |  |  |  |

| Output Amplitude Word                    | AMPL_WIDTH     | Integer    | 16    | Bits  |  |  |  |  |  |  |  |

| Frequency Re            | quire | ed | ]     | FTW       | FTW<br>actual      | Frequency<br>Generated                  | Actual Frequency<br>Simulation | from |

|-------------------------|-------|----|-------|-----------|--------------------|-----------------------------------------|--------------------------------|------|

| 5MHz                    |       |    |       | 170.66    | 171                | 5.00MHz                                 | 5.00MHz                        |      |

| Current Sin<br>Time: 10 |       |    | 1     | 00 ns 200 | ns 300 ns          | 400 ns 500 ns 600 n                     | s 700 ns 800 ns 900 ns         |      |

| ò, cik                  |       | 0  |       |           |                    |                                         |                                |      |

| 6. reset                |       | 0  |       |           |                    |                                         |                                |      |

| nco_f                   | tw    | 2  |       |           |                    | 24h155555                               |                                |      |

| _ 000 😽 🗖               | pbw   | 1  |       |           |                    | 121000                                  |                                |      |

| _ 🖬 😽 nco_              | phas  | 1_ | 12h00 | • 1000    | <b>TERRETORIES</b> |                                         | <b>CONTRACTORIZATION</b>       |      |

| ■ <mark>81</mark> nco_s | ampl  | 1  | 1610  | 00 XXXX   | 000000000          | 000000000000000000000000000000000000000 | <b>EXCLUSION CONTRACTOR</b>    |      |

| ■ <mark>%(</mark> nco_s | ampl  | 1  | 16100 | • XXXX    | 00000000           | 000000000000000000000000000000000000000 | <u>ENERGENERGENERGENER</u>     |      |

|                         |       |    |       |           |                    |                                         |                                |      |

TABLE 2: VHDL simulation results are shown below:

Fig. 3: Simulated output of DDS

| Current Simulation<br>Time: 1000 ns |   |       | 10 ns |    | 2   | 00 ns        |    |     | 300 | ns<br>I |     | 40 | 00 ns |     | 8   | 00 ns |    |     | 500 n | :<br> |     | 700 n<br>I |   |     | 900 r           |     | 900     |

|-------------------------------------|---|-------|-------|----|-----|--------------|----|-----|-----|---------|-----|----|-------|-----|-----|-------|----|-----|-------|-------|-----|------------|---|-----|-----------------|-----|---------|

| 🖬 💱 nco_phas                        | 1 |       |       | ΟD | ĊĊ. | XX           | Ō  | DÖ  | Ò   | X       | DΟ  | ΟÒ | ĊĊ    | ĊΫ  | Ń   | XX    | Ċ  | XO. | XX    | X     | 00  | ĊĊ         | X | ΩÈ  | ĊĊ              | ΟÖ  | DOD     |

| 💦 nco_p                             | Q |       |       |    |     |              |    |     |     |         |     |    |       |     |     |       |    |     |       |       |     |            | 1 |     |                 |     |         |

| 🛃 nco_p                             | 1 |       |       |    |     |              |    |     |     |         |     |    |       |     |     |       |    |     |       |       |     |            |   |     |                 |     |         |

| 🚵 nco_p                             | 1 |       |       |    |     |              | Π  |     |     |         |     |    |       |     |     |       | Π  |     |       |       |     |            |   |     |                 |     |         |

| 🛃 nco_p                             | 0 |       |       |    |     |              |    |     |     |         |     |    |       |     |     |       |    |     |       |       |     |            |   |     |                 |     |         |

| 💦 nco_p                             | 1 |       |       |    |     |              | Π  |     |     |         |     |    |       |     |     |       |    |     |       |       |     |            |   |     |                 |     |         |

| anco_p                              | 0 |       |       |    |     |              | ٦  |     | ٦   |         |     |    |       | ٦   |     |       |    |     |       |       |     |            |   | Ш   |                 |     |         |

| 🛃 nco_p                             | 1 |       |       |    |     |              |    |     |     |         |     |    |       |     |     |       |    |     |       |       |     |            |   |     |                 |     |         |

| nco_p                               | 0 |       |       |    |     |              | ٦  |     | ٦   | Г       |     |    |       |     |     |       |    |     |       |       |     |            |   |     |                 |     |         |

| 👌 nco_p                             | 1 |       |       |    |     |              | Π  |     |     |         |     |    |       |     |     |       |    |     |       |       |     |            | 1 |     | UT              |     |         |

| 💦 nco_p                             | 0 |       |       |    |     |              |    |     |     |         |     |    |       |     |     |       |    |     |       |       |     |            |   |     |                 |     |         |

| 👌 nco_p                             | 1 |       |       |    |     |              |    |     |     |         |     |    |       |     |     |       |    |     |       |       |     |            |   |     |                 |     |         |

| 🛃 nco_p                             | 0 |       |       |    |     |              |    |     |     |         |     |    |       |     |     |       |    |     |       |       |     |            |   |     |                 |     |         |

| 🛙 🚮 nco_ampl                        | 1 | 67600 |       | T  | 0.0 | $\mathbf{T}$ | 10 | 0.0 | C)  | 303     | D.D | 00 | OC.   | CT. | 303 | TT.   | C1 | 313 | D.D.I | 30    | 0.0 | D.D.       |   | TT. | $\overline{00}$ | 0.0 | D.D.D.I |

Fig. 4: Phase Simulation of DDS

| Current Simulation<br>Time: 1000 ns | 3 | 6ma<br>Uns 100ns | 2007 | IS 300 | ns 400 | ns 500 | ns 600 | ns 700 i | ns 800 r | ns 900.ns |

|-------------------------------------|---|------------------|------|--------|--------|--------|--------|----------|----------|-----------|

| nco_ampl                            | 1 | 16%0000          | 0000 |        | 000000 | 000000 | 000000 | 000000   | 000000   |           |

| al nco_a                            | 0 |                  |      |        |        |        |        |          |          |           |

| àl nco_a                            | 0 |                  |      |        |        |        |        |          |          |           |

| òl nco_a                            | 0 |                  |      |        |        |        |        |          |          |           |

| òl nco_a                            | 0 |                  |      |        |        |        |        |          |          |           |

| onco_a                              | 0 |                  |      |        |        |        |        |          |          |           |

| l nco_a                             | 0 |                  |      |        |        |        |        |          |          |           |

| l nco_a                             | 0 |                  |      |        |        |        |        |          |          |           |

| 👌 nco_a                             | 0 |                  |      |        |        |        |        |          |          |           |

| 👬 nco_a                             | 0 |                  |      |        |        |        |        |          |          |           |

| 👌 nco_a                             | 0 |                  |      |        |        |        |        |          |          |           |

| dinco_a                             | 0 |                  |      |        |        |        |        |          |          | أكرليل    |

| al nco_a                            | 0 |                  |      |        |        |        |        |          |          | أراراي    |

| l nco_a                             | 0 |                  |      |        |        |        |        |          |          |           |

Fig. 5: Amplitude Simulation of DDS

### IV. Conclusion

The performance of Direct Digital Synthesizer is done at tuning frequency which is specified as normalized value relative to clock rate given. Since it is dual Oscillator, hence it support variable Width, Phase modulation inputs and user defined frequency resolution. Here, the outputs of DDS can be adjusted over a wide range of frequencies with high degree of resolution.

### V. Future Work

With a DDS, if the system operates at all, it works perfectly – there's never any tuning or component tolerance to worry about. As rate is programmable, it supports logic functions that would be extremely difficult to emulate with discrete logic gates. The design of code requires hardware with more resources as it exceeds the capacity of lower FPGA devices.

### References

- [1] Xilinx LogiCORE, Digital Up Converter (DUC) v1.4, DS276 May 23, 2005 www.xilinx.com.

- [2] Lattice Semiconductor Corporation, The FPGA as a Flexible and Low-Cost Digital Solution for Wireless Base Stations, A Lattice Semiconductor White Paper, March 2007.

- [3] Matthew P. Donadio, CIC Filter Introduction, For Free Publication by Iowegian, m.p. donadio@ieee.org, 18 July 2000.

- [4] Pavel KOVAR, Generation of the Narrow Band Digital Modulated Signals Using Quadrature Digital Up Converter, *RADIO* ENGINEERING, VOL. 12, NO. 1, APRIL 2003.

- [5] Direct digital synthesis (DDS) http://www.radioelectronics com/info/receivers/synth\_basics/dds.php.

- [6] QAN19 Modulating Direct Digital Synthesizer in a quick logic FPGA . http://www.quicklogic.com/images/appnote19.pdf (Accessed on April 10, 2006.)

- [7] Eva Murphy and Colm Slattery, All about Direct Digital Synthesis, Analog dialogue 38-08, August 2004, http://www.analog.com/analogdailogue

- [8] Xilinx LogiCORE, Multiply Accumulator v4.0, DS336 April 28, 2005 www.xilinx.com.

- [9] Cyril Prasanna Raj P and Subash, SASTech Journal, Vol 4. PP 33-39, September 2006.

- [10] S. Signell, T. G. Kouyoumdjiev, K. H. Mossberg, Design and Analysis of Bilinear Digital Ladder Filters, IEEE Trans. on Circuits and Systems, Vol. 43, No. 2. February 1996.